Final Year Project: Week 3 and Week 4

Week3

Introduction to Verilog Hardware Descriptive Language (Verilog HDL)

1.Hardware Description

Languages

- A

hardware description language is a computer language that is used to describe hardware.

- Two

HDLs are widely used :Verilog HDL and VHDL (Very High

Speed Integrated Circuit Hardware Description Language).

- Schematic

design entry can be replaced by writing HDL code that CAD tools understand.

- CAD

tools can verify the HDL codes, and create the circuits automatically from HDL

codes.

2. Fact about Verilog

History of Verilog

- In 1980s, originally developed by Gateway Design Automation.

- In 1990, was put in public domain.

- In 1995, adopted as an IEEE standard 1364-1995

- In 2001, an enhanced version, Verilog 2001

3.Functions

of Verilog HDL

- Design entry (using schematics or

HDL)

- Simulation and verification of

the design

- Synthesis

4.Design Flow Using Quartus II Verilog HDL

and DE2 Board:

Week 4

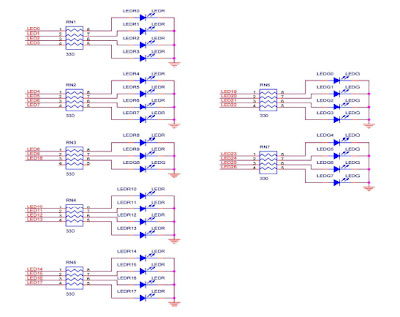

1.Create simple design entry using Verilog code to make more understand

with Verilog HDL. The Verilog code, design entry , and successful compiling the design circuit shown as below:

|

| Verilog code |

|

| Design entry |

|

| Successful compiling the design circuit |

2. Pin Assignment: During the compilation above, the Quartus II Compiler was free to choose any pins on the selected FPGA to serve as inputs and outputs.However, the DE2 board has hardwired connections between the FPGA pins and the other components on the board.I will use two toggle switches, labeled SW1 and SW0, to provide the external inputs, x1 and x2, to the circuit. These switches are connected to the FPGA pins N26 and N25, respectively. I will connect the output f to the green light-emitting diode labeled LEDG0, which is hardwired to the FPGA pin AE22.

|

| The available pins. | | | | | |

|

| The complete assignment. |

3. Performing the simulation: Typically, functional simulation is used to verify the functional correctness of a circuit as it is being designed.The result of timing simulation as shown below:

|

| Result of timing simulation. |

4. Programming and Configuring the FPGA Device: The FPGA device must be programmed and configured to implement the designed circuit. The required configuration file is generated by the Quartus II Compiler Assembler module. The configuration data is transferred from the host computer (which runs the Quartus II software) to the board by means of a cable that connects a USB port on the host computer to the left most USB connector on the board by using USB-Blaster driver installed. Connected the USB cable and turn on the power supply switch on the board.The programming and configuration task is performed as follows:

|

| The Programmer window. | | | | |

|

| The Hardware Setup window. |

|

| The Programmer window upon completion of programming |

5. Testing the Designed Circuit: Having downloaded the configuration data into the FPGA device, the implemented circuit have tested. The result is the circuit implements is similar the truth table. Its success.